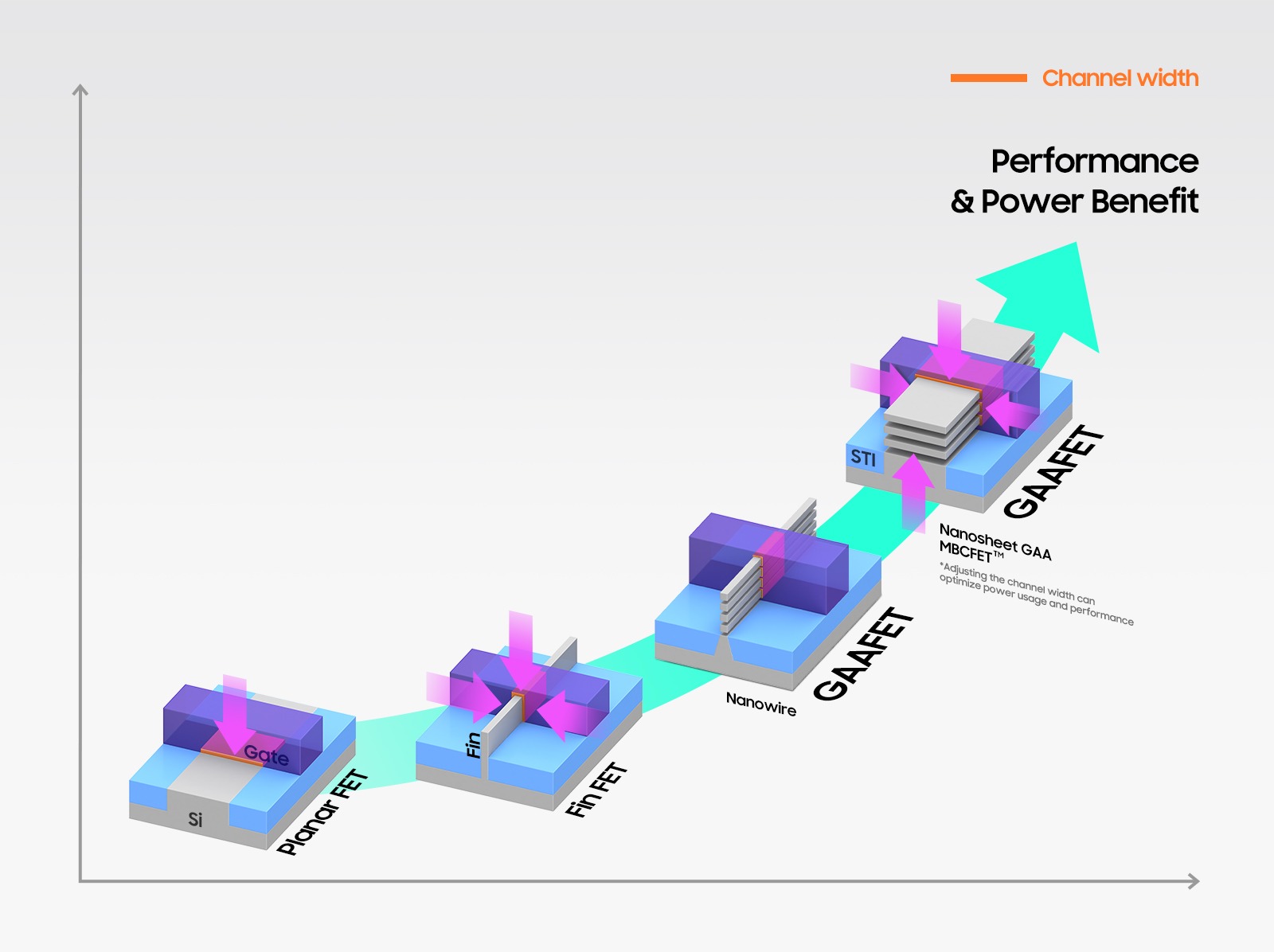

La division semi-conducteurs Samsung Foundry a annoncé avoir commencé la production de puces 3 nm dans son usine de Hwasong. Contrairement à la génération précédente, qui utilisait la technologie FinFet, le géant coréen utilise désormais une architecture de transistors GAA (Gate-All-Around), qui augmente considérablement l'efficacité énergétique.

Les puces de 3 nm dotées de l'architecture GAA MBCFET (Multi-Bridge-Channel) gagneront en efficacité énergétique, entre autres, en réduisant la tension d'alimentation. Samsung utilise également des transistors à nanoplaques dans les puces semi-conductrices pour les chipsets de smartphones hautes performances.

Par rapport à la technologie des nanofils, les nanoplaques dotées de canaux plus larges permettent des performances plus élevées et une meilleure efficacité. En ajustant la largeur des nanoplaques, les clients Samsung peuvent adapter les performances et la consommation électrique à leurs besoins.

Vous pourriez être intéressé par

Selon Samsung, par rapport aux puces 5 nm, les nouvelles ont des performances 23 % plus élevées, une consommation d'énergie 45 % inférieure et une surface 16 % plus petite. Leur 2e génération devrait alors offrir des performances 30 % supérieures, une efficacité 50 % supérieure et une surface 35 % plus petite.

« Samsung connaît une croissance rapide alors que nous continuons à démontrer notre leadership dans l'application des technologies de nouvelle génération dans le secteur manufacturier. Nous visons à poursuivre ce leadership avec le premier processus 3 nm avec l'architecture MBCFETTM. Nous continuerons à innover activement dans des développements technologiques compétitifs et à créer des processus qui contribueront à accélérer l’atteinte de la maturité technologique. a déclaré Siyoung Choi, responsable de l'activité semi-conducteurs de Samsung.